广西类脑计算与智能芯片重点实验室(BCIC)黎海生教授和清华大学龙桂鲁教授团队在量子计算领域的最新研究成果——题为《The circuit design and optimization of quantum multiplier and divider》(量子乘法器和除法器的电路设计与优化)的学术论文在国际学术期刊《SCIENCE CHINA-Physics, Mechanics & Astronomy》(中科院升级版1区,JCR Q1,Top期刊)上发表。

论文简介

在噪声存在的情况下,需要容错电路来进行稳健的量子计算。基于Clifford+ T门的量子电路是实现容错计算的、易接受的方法之一。因此,减小T深度、T计数和电路宽度成为Clifford+ T电路重要的优化目标。本文综合考虑电路宽度、T深度、T计数,分别设计并优化两个乘法器乘数和一个除法器,希望为量子运算器的容错实现提供一种可行的技术手段。

主要工作

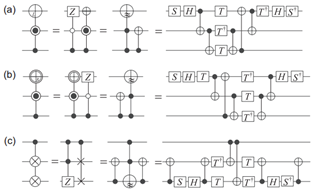

(1)设计了近似Toffoli门, Peres门和TR门的Clifford+ T电路,它们的T深度和T计数分别为2和4。因而,提出的实现电路比相应的Toffoli门, Peres门和TR门有更低的T深度和T计数。

图1. 近似Toffoli门及其变体

图2. 近似Peres、TR、和Fredkin门

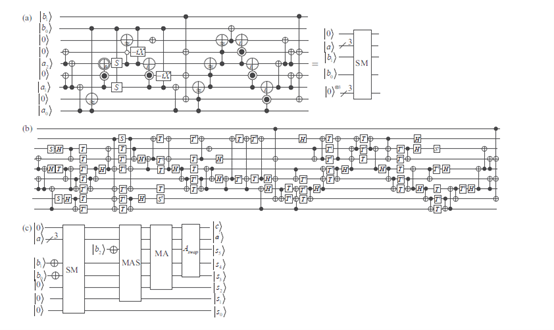

(2)利用近似Toffoli门, Peres门和TR门,设计了两个量子乘法器。对比已有的量子乘法器,提出的第二个量子乘法器大约减少了77% T深度,60% T计数和25%电路宽度。

图3. 量子乘法器电路

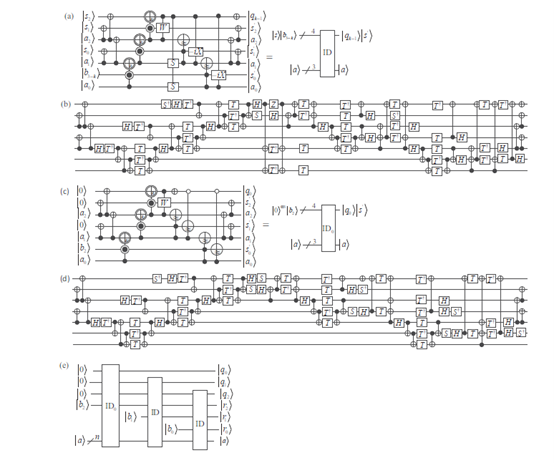

(3)设计的除法器在T深度、T计数和、电路宽度方面都优于已有的量子除法器。

图4. 量子除法器电路

结论

提出了近似Toffoli、Peres 和TR门的Clifford + T电路。然后,利用提出的近似门,设计了乘法器和除法器。通过对比分析,所提出的乘法器和除法器有低的电路宽度、T深度和T计数。

原文连接:https://link.springer.com/article/10.1007/s11433-021-1874-2